1. Tujuan

- Mengetahui definisi logika PMOS dan NMOS

- Mengetahui karakteristik dan perbedaan PMOS dan NMOS

2. Alat dan Bahan

I. Alat

a. Power Supply

Power Supply atau dalam bahasa Indonesia disebut dengan Catu Daya adalah suatu alat listrik yang dapat menyediakan energi listrik untuk perangkat listrik ataupun elektronika lainnya.

b. PMOSFET

PMOS atau PMOS logika (dari P-channel metal-oxcide semiconductor ) adalah keluarga dari rangkaian digital berdasarkan p-channel , modus perangkat logam oksida semikonduktor transistor efek medan (MOSFET).

c. NMOS

Logika nMOS adalah gerbang logika yang menggunakan transistor

efek medan semikonduktor oksida logam (MOSFET) untuk membentuk fungsi

gerbang logika dan sirkuit digital lainnya.

MOSFET tipe-n disusun dalam bentuk "jaringan pull-down" (PDN) di antara

keluaran gerbang logika dan tegangan catu negatif, dimana sebuah

resistor diletakkan di antara keluaran gerbang logika dan tegangan catu

postif. Sirkuit didesain sedemikian rupa sehingga jika keluaran adalah

rendah (logika 0), sirkuit PDN akan aktif, membuat jalan arus antara

catu negatif dengan keluaran.

d. Ground

Ground adalah suatu system instalasi listrik yang bisa meniadakan beda potensial sebagai pelepasan muatan listrik berlebih pada suatu instalasi listrik dengan cara mengalirkannya ke tanah.

3. Dasar Teori

Logika PMOS

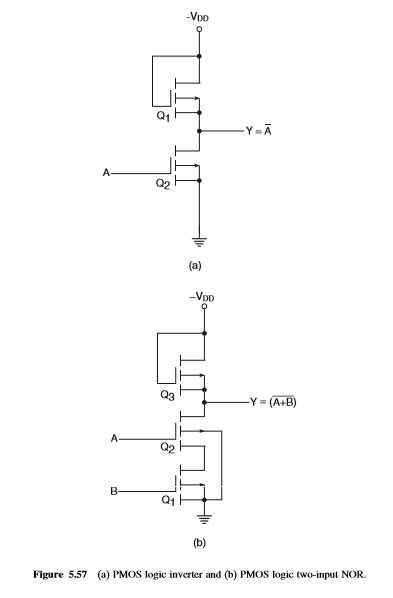

Keluarga logika PMOS menggunakan MOSFET saluran-P. Gambar 5.57 (a) menunjukkan rangkaian inverter menggunakan logika PMOS. MOSFET Q1 bertindak sebagai beban aktif untuk sakelar MOSFET Q2. Untuk rangkaian yang ditunjukkan, GND dan −VDD masing-masing mewakili logika '1' dan logika '0' untuk sistem logika positif. Ketika input di-ground (yaitu logika '1'), Q2 tetap dalam cut-off dan −VDD muncul pada output melalui Q1. Ketika input berada pada −VDD atau dekat −VDD, Q2 berjalan dan output mendekati potensial nol (yaitu logika '1').

Gambar 5.57 (b) menunjukkan gerbang NOR dua input berbasis logika PMOS. Dalam susunan logika pada Gambar 5.57 (b), output beralih ke status logika '1' (yaitu potensial tanah) hanya ketika Q1 dan Q2 berjalan. Ini hanya mungkin jika kedua input berada dalam status logika '0'. Untuk semua kombinasi masukan lain yang mungkin, keluaran berada dalam status logika '0', karena, dengan Q1 atau Q2 nonkonduktor, keluarannya hampir -VDD melalui Q3 konduksi.

Sirkuit pada Gambar 5.57 (b) berperilaku seperti gerbang NOR dua masukan dalam logika positif. Dapat disebutkan di sini bahwa MOSFET yang digunakan sebagai beban [Q1 pada Gambar 5.57 (a) dan Q3 pada Gambar 5.57 (b)] dirancang sedemikian rupa sehingga memiliki resistansi ON yang jauh lebih besar daripada total ON- resistansi dari MOSFET yang digunakan sebagai sakelar [Q2 pada Gambar 5.57 (a) dan Q1 dan Q2 pada Gambar. 5.57 (b)].

Logika NMOSKeluarga logika NMOS menggunakan MOSFET N-channel. Perangkat MOS saluran-N memerlukan area chip yang lebih kecil per transistor dibandingkan dengan perangkat saluran-P, sehingga logika NMOS menawarkan kepadatan yang lebih tinggi. Juga, karena mobilitas pembawa muatan yang lebih besar di perangkat saluran-N, keluarga logika NMOS juga menawarkan kecepatan yang lebih tinggi. Karena alasan inilah sebagian besar perangkat memori dan mikroprosesor MOS menggunakan logika NMOS atau beberapa variasinya seperti VMOS, DMOS dan HMOS. VMOS, DMOS dan HMOS hanyalah variasi struktural dari NMOS, yang bertujuan untuk lebih mengurangi penundaan propagasi. Gambar 5.58 (a), (b) dan (c) masing-masing menunjukkan inverter, NOR dua masukan dan NAND dua masukan menggunakan logika NMOS. Sirkuit logika sudah cukup jelas.

4. Percobaan 4.1 Prosedur Percobaan

- Gunakan softeware Proteus/Multisim

- Persiapkan alat dan bahan (komponen)

- Rancang rangkaian seperti pada gambar

- Jalankan rangkaian

- Analisa apa yang terjadi

4.2 Gambar Rangkaian

|

| Figure 5.57 (a) PMOS logic inverter and (b) PMOS logic two-input NOR. |

|

| Figure 5.58 (a) NMOS logic circuit inverter, (b) NMOS logic two-input NOR and (c) NMOS logic two-input NAND. |

4.3 Prinsip Kerja Rangkaian

Figure 5.57

Gambar 5.57 (a) menunjukkan rangkaian inverter menggunakan logika PMOS.

MOSFET Q1 bertindak sebagai beban aktif untuk sakelar MOSFET Q2. Untuk

rangkaian yang ditunjukkan, GND dan −VDD masing-masing mewakili logika '1' dan

logika '0' untuk sistem logika positif. Ketika input di-ground (yaitu logika '1'), Q2

tetap dalam cut-off dan −VDD muncul pada output melalui Q1. Ketika

input berada pada −VDD atau dekat −VDD, Q2 berjalan dan output mendekati

potensial nol (yaitu logika '1').

Gambar 5.57 (b) menunjukkan gerbang NOR dua

input berbasis logika PMOS. Dalam susunan logika pada Gambar 5.57 (b), output

beralih ke status logika '1' (yaitu potensial tanah) hanya ketika Q1 dan Q2

berjalan. Ini hanya mungkin jika kedua input berada dalam status logika '0'.

Untuk semua kombinasi masukan lain yang mungkin, keluaran berada dalam status

logika '0', karena, dengan Q1 atau Q2 nonkonduktor, keluarannya hampir -VDD

melalui Q3 konduksi.

Figure 5.58

Gambar 5.58 (a), (b) dan (c) masing-masing menunjukkan inverter, NOR dua masukan dan NAND dua masukan menggunakan logika NMOS. Ketika logicstate berlogika 1, maka outputny adalah 0, begitu sebaliknya. Hal tersebut berlaku untuk ketiga rangkaian.

4.4 Video Simulasi

Figure 5.57

Figure 5.58

5. Download File

File HTML - Download

File Rangkaian gambar 5.57 - Download

File Rangkaian gambar 5.58 - Download

File Video gambar 5.57 - Download

File Video gambar 5.58 - Download

Tidak ada komentar:

Posting Komentar